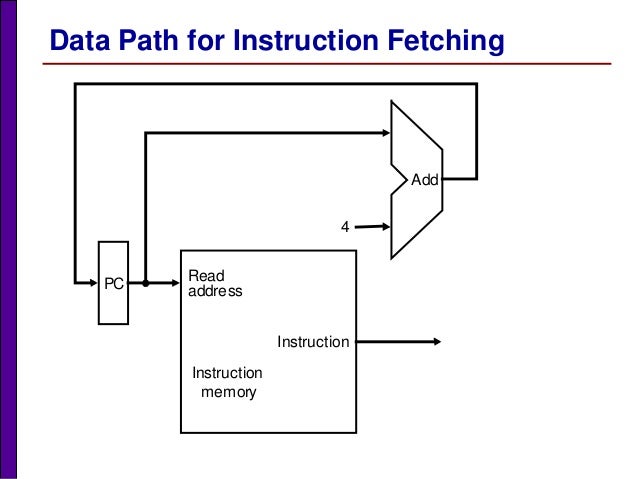

load the MAR with the PC address, increment the PC, load from memory into the ALU right input, load from register C into the ALU left input, set the ALU mode to ADD, store from the ALU output into register C.load the MAR with the PC address, increment the PC, and load from memory into the opcode register.An instruction like ADD BC, 1234 might process the bytes like this: Instead, the instructions are designed so only the opcode needs to be stored in the opcode register is needed, and the operand bytes can go directly to their final destination. But 8-bit CPUs generally do not have 3-byte instruction registers. In the 8-bit era it was typical that a CPU would read a 1-byte opcode, and then the operands (if any) would be in the next 1 or 2 bytes.Īlmost. So multi-byte instructions are a necessity. If they have 4-bit operands (not enough) you can only fit 16 instructions (also not enough). You can only fit 256 instructions, in fact. The instructions are often bigger than they need to be, but the simplicity can be worth it.Ĩ-bit processors don't do this, because you can't really fit enough instructions in only 8 bits. All the instruction operands are included as part of the instruction. This works for them because 32 bits is enough to fit plenty of instructions, and it makes it easy for the processor to load instructions. Some processors - generally, 32-bit RISC ones - make sure that all instructions fit in one location in memory. I would appreciate feedback on any of these questions. Or, is there a different way to store the instructions to get around this? Just to note, my processor also doesn't use any caching, meaning it has to get instructions and data exclusively from RAM.Īlso, how would this work for jump instructions? If I want to jump to a specific instruction in the program, but don't know the address in memory because of all the other multi-length instructions. loading the MAR with the PC address, incrementing the PC, and loading from memory into part of the instruction register, repeated up to three times. However, when fetching an instruction from memory, does this mean that the processor has to make up to 3 memory calls just for the fetch stage? For example, a 2 byte instruction could store the opcode-byte in one address, and a one-byte data value in the following. I've been researching, and I found that instructions generally span across multiple addresses in memory. The address length of 14 bits, and an instruction lengths ranging from 1 to 3 bytes.

#Cpusim instruction memory how to

It doesn't make use of anything advanced as pipelining, as my knowledge isn't at that level yet to know how to implement it. For more information, refer to the GPU Sprites TypeData documentation.I've recently been designing a simple 8-bit microprocessor, similar to the Intel 8008. If you are using incompatible modules in your Emitter, those modules will be highlighted in red. To use these particles, right-click on the empty space under the Emitter header and select Type Data > New GPU Sprites:īear in mind that some modules will not support GPU particles. This of course will significantly change the way we approach doing effects such as snowfall, rain, or sparks. However, what they lack in supported features they more than make up for in sheer numbers the GPUSprite TypeData allows you to spawn tens to hundreds of thousands of particles without a severe performance impact. Some of the features available in the CPU particles (such as light emission, Material parameter control, and Attraction modules to name a few) are not supported in GPU particles.

Notice that the fountain on the right - which uses GPU particles - is outputting significantly more particles than the other.ĬPU and GPU sprites behave similarly, but they have some key differences. This first effect shows off two very simple particle fountains, one created via standard CPU particle sprites and the other via GPU sprites. The benefit to this is that since the GPU is handling the calculation, many thousands more particles can be processed at once, allowing for much denser and more detailed particle systems.

These are particles that are first spawned on the CPU, but then processed and calculated entirely by the graphics card. One of the particle types available in Unreal Engine 4 is GPU Sprites.

0 kommentar(er)

0 kommentar(er)